根据具体运算操作而修改其硬电路的计算机正在开辟一个计算机设计的新纪元。由于这类计算机能够快速过滤数据而适用于模式识别、图象处理以及加密等领域。

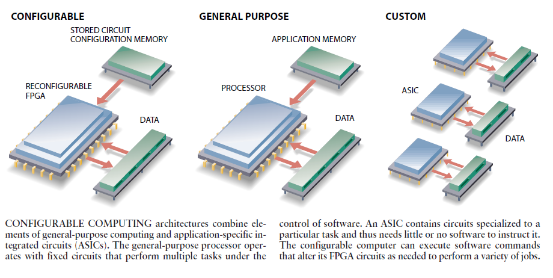

计算机设计人员经常面临在速度与通用性方面寻求适当平衡的抉择。他们要么可以制造出能执行多种不同功能的通用芯片,但速度相当慢;要么可以制造出仅用于完成有限的一组任务的特定应用芯片,而执行速度却快得多。微处理器(例如,通常在个人计算机上看到的Intel公司的Pentium或Motorola公司的PowerPC芯片)就是采用的通用芯片,即以二进制格式编码的程序指令可使微处理器实际上完成程序员可设想的住何逻辑或算术运算。例如,Intel公司的Pentium芯片决不是专为运行微软公司的Word或计算机游戏“DOOM”而设计的,但是二者皆可在其上运行。

相反,往往被称为专用集成电路(ASICs)的定制的硬件电路的确提供了某项特定任务所需的功能。对某项给定的作业通过仔细调整每一个ASIC,计算机设计人员就可以设计出更小、更便宜且更快速的芯片,其耗电量低于可编程处理器。例如,用于PC机上的专用图形芯片能够比通用中央处理器快10到100倍的速度在计算机屏幕上画线或对图象着色。

当设计人员在通用性与速度之间作出选择时,他们还必须考虑费用问题。一个设计精良的ASIC将解决它当初给设计规定的问题,但在ASIC设计完成后可能会出现不少的改进问题。另外,即使可以研制出针对新问题的改良型ASIC,但是原来的硬件电路可能太过于专一化而不能在其后续的换代产品中重新使用。因此设计和制造某个ASIC所需的技术工作必须通过采用过少量的部件来得到补偿。

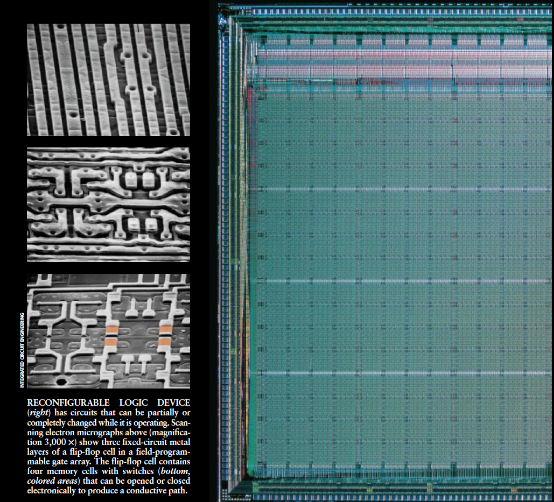

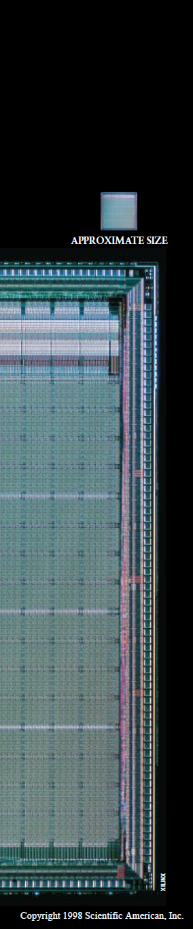

集成电路领域中的一项新的发展提供了第三种选择;即大规模的,快速的,现场可编程的门阵列,或简称为FPGAs——这是一种几乎能在使用中的任何地方进行修改的易调整硬件电路。FAGAs由可配置的逻辑块阵列组成,这些逻辑块可执行逻辑门的功能。逻辑门就如同带有多个输入和单一输出的开关。它们用于数字电路中来执行基本的二进制运算,例如与(AND),与非(NAND),或(OR),或非(NOR)以及异或(XOR)等运算。今天用于计算的大多数硬件中,门电路的逻辑功能是固定的且不能进行修改。但是,在FPGAs中,不仅在逻辑块中执行的逻辑功能而且逻辑块之间的连接部分均能通过向芯片发送信号来改变。这些逻辑块在结构上类似于某些ASIC中用的门阵列,但是标准的门阵列是在制造期间已配置好了的,在FPGAs中的可配置逻辑块可以在集成电路出厂后的很长时间里被反复地重新布线重新编程。

使这种可配置的计算成为可能的关键在于设计新的FPGAs,这类新FPGAs能极快地被配置。最早期的现场可编程阵列需要几秒或更多的时间来改变其接线——非常适合那些想测试可更换线路装置的工程师们从及对那些售出的设备偶尔需要更新的公司。新一代的FPGAs能够在一毫秒内完成配置,我们期待着到在两年内能生产出配置时间仅100微秒的FPGAs。最终计算设备也许能几乎不断地根据输入数据或微处理环境的改变而适应其硬件。

FPGA的设计多种多样,但其基本结构是由大量的可配置逻辑块和一个可编程的接线网组成,该接线网能把这些逻辑块按设计人员选定的任意模式连接起来。那些粗晶粒结构的FPGAs具有少量的而功能强大的可配置逻辑块;那些细晶粒结构的FPGA,则具有很多但简单的逻辑块。粗晶粒FPGA中的单个元件可以进行两个数相加或比较的操作。而细晶粒FPGA中的一个逻辑块只能进行两个二进制数的比较——事实上它应该是一个单逻辑门。设计人员首先可根据当前的应用程序以及建立复杂的子系统允许的时间来选择粗晶粒芯片或者细晶粒芯片。

计算装置可以以多种不同的方式利用可配置元件,最起码要求的技术是按照命令切换功能——等价于退出一个程序然后运行另一个程序的硬件。按几秒量级的慢速配置,在这种应用中是完全可以接受的。更快的编程时间允许动态结构交换;即单个FPGA接二连三地执行一系列任务。在每项任务间对自身进行重配置。这样的结构以分时模式操控芯片,而且连续配置之间的交换如此快速以致于看上去FPGA是同时完成所有功能的。

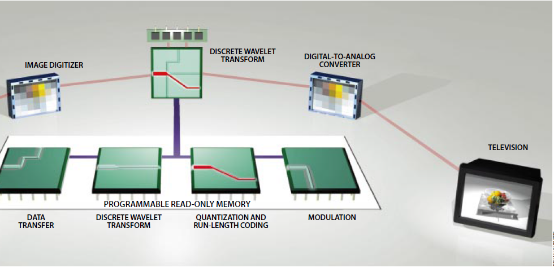

采用这种方法,我们已经制造出了一套单芯片的视频传输系统,该系统可在每视频帧进行四次自身重配置。因此,它只需要固定式ASIC芯片所需硬件的四分之一,FPGA首先把输人的视频信号存储在存储器中,然后运用两种不同的图象处理转换技术,最后将其自身转换到发送信号的调制解调器。

最具挑战性和潜力最大的可配置计算的形式涉及在执行某项任务进程中硬件本身的重新配置,所以为了适应提高后的性能,要改进其自身的程序设计。图象识别芯片可根据其所注视的对象的初步识别而自身进行调整:如果一幅图象包含轿车或卡车,那么原来打算跟踪高速飞行的飞机或慢速移动的人的部分电路就会重新配置来跟踪陆地上的车辆。对某些应用来说,这种对传统计算机设计的主要变更能够制造出比用通用微处理器或定制的芯片快得多且更通用的机器设备。而在传统的计算机设计中,硬件一开始就被规定好了的。

削减关键的硬件

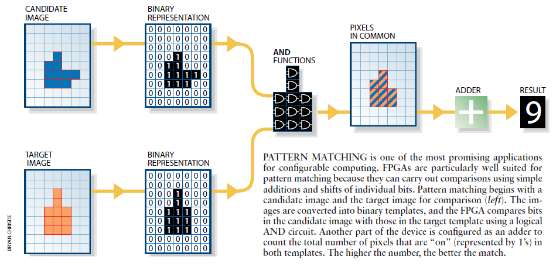

可配置计算的一项最有前途的应用涉及模式匹配。模式匹配应用于诸如笔迹识别、脸形鉴别、数据库检索以及目标自动识别。模式匹配的一项基本操作就是把输入的一组数位(表示一幅图象、一串字符或其它数据)与对应于可能要识别的模式的一组模板进行比较。当输入的与该模板中的数位相匹配的数位数目超过某一阈值时系统就宣告识别成功。

在目标识别的情况中——如推动我们初期工作的军事应用中——最大的挑战是输人图象与数千个模板进行快速比较。例如,某个模板可能表示特定类型车辆的前视或侧视图。每幅图象通常包含数千个象素(图象元素),并且目标物可能出现在图象中的任何位置。对军事应用而言,需要尽快识别出目标,系统就需要以每秒数万亿次的运算速度来进行比较,因为输入图象中的所有象素须与众多模板的所有象素进行比较。

在国防高级研究项目局(DARPA)的支持下,我们制造了一套带有可配置硬件的原型识别系统,该系统通过依次对每个模板自身调整达到有效地节省硬件。典型模板中的许多象素对匹配的结果并不起作用(见下页底部的示意图),因此可配置计算的机器可简单地从其计算中省略掉这些象素。常规的系统不能用类似的方法轻易地减少它自身,因为要省略的象素随模板而异。我们可通过利用模板间的相似性调整硬件以进一步开发可配置机器的灵活性。这种可配置的硬件可并行地处理一组模板,对该组模板中其值相同的每个象素只使用一个比较部件。例如,单个电路就能够研究某个象素,然后把其结果传送给其它七个模板而不用让八个单独的硬件电路来研究八个不同模板中的某个象素。

最近,我们又制造了一套原型的加密系统(也由DARPA资助),该系统同样利用了可配置硬件的优点。FPGA执行数据加密标准(DES),使用56位长的密匙来加密64位长的数据块(加密的密匙就是一个用于对保密信息进行编码或解码的数字)。DES加密通常分两步进行,即子密匙的调度和数据处理。在第一步中,一组交替与置换操作将56位的加密密匙转换成一连串的16个子密匙。然后每个子密匙按单独一轮处理数据;每个64位的数据块整个要进行16轮加密或解密。当计算机同时处理多个用户时,用户问的每次对话必须有不同的密匙,并且当部分信息到达不同用户时加密硬件将会改变密匙。

在DES的众多应用中,在一长数据块通过数据路径时加密密匙保持不变。例如,如果有两人正在安全的网络上进一行通信,他们变换安全加密密匙一次。然后在他们对话的整个期间都使用这个密匙来生成每轮的加密或解密的子密匙,有些ASIC设计成只处理一种加密算法,例如DES,而其它的一一例如可编程数字信号处理器——则能够执行多种加密算法。

用可配置的芯片,软件可计算子密匙的值一次,而且数据处理电路可因这些特定的子密匙而被优化。这种方法使子密匙调度硬件可从系统中完全去掉、这一节约使我们可以用13000门的FPGA来执行DES算法,而在以前则需要25000的电路,当必须改变加密密匙时,用户可以立即指定一个新电路,定制成新密匙然后把它下载到FPGA中。我们所制造的目标识别系统及加密系统的原型有助于说明当计算机中的硬件能定制成各种多变的外部数据设备时所带来的巨大活性。有许多其它的应用将能够从按这种方式改进计硬件的能力中得益,其中包括数字通信、设计过程自动化以及用于雷达的数字滤波等。

可配置计算的未来

可设置计算机仍然是一个及其崭新的领域。虽然在洛杉矶的加利福利亚大学的Gerald Estrin 早在60年代末就突出了可配置计算的设想,但是第一台样机知道几年前才出现,而且目前具有多达100000个逻辑元件的FPGA仍离把该技术的全部潜力开发出来的目标相差甚远。未来的FPGA会大得多,正如许多其他的集成电路一样,单个FGGA上的元件数目几乎每隔18个月就要增加一倍。我们期望在本世纪末前看到拥有一百万个逻辑元件的FPCA芯片出现。这样的芯片将会有更广泛的应用,包括高度复杂的通知及信号处理算法。

研究人员及制造厂商正在克服阻碍采用可配置计算的许多其他设计方面的限制。用目前的FPGA并非能有效地进行所有的运算;它们非常适合由位级运算组成的算法,例如模式匹配以及整数运算,但不适合数值运算,例如高精度的乘法或浮点运算。诸如那些用于被处理器和数字信号芯片中的专用乘法电路可进行优化使其比由FPGA芯片中的可配置逻辑块构成的乘法电路更有效地执行运算。此外,FPGA芯片上目前只提供非常少的内部存储器来存储计算的当前结果,因而许多可配置的计算运用需要大量的外部存储。数据进出FPGA的传送会增加耗电量并可能降低运算速度。

幸好研究人员正在研制包含存储器、运算处理单元及其它专用电路块的高级FPGA芯片。马萨诸塞技术研究所的Andre Dohon和Thomas F. Knight提出了一种在一系列存储器中存储多种配置的FPGA芯片,在数十或数百纳秒数星级的单个时钟周期内,这种芯片可以在不丢失部分已处理的数据情况下,从一种配置转换为另一种配置。

同时布雷汉姆˖扬大学的Brad L. Hutchings已经使用可配置计算制造出一台动态指令集计算机(DISC),它使微处理器有效地与FPGA相结合且表明利用存储配置的方法来进行自动重配置的潜力,当一个程序运行时,如果指定的电路不存在,则FPGA就要求重新配置。DISC允许设计人员创建和存储大量的电路配置并在需要时激活它们,这就如同程序员将初始化微处理器中的某个软件子程序的调用一样。

由维吉尼亚工业学院和州立大学的Peter M.Athanas领导的Coat研究小组正在研究称为蛀孔(Wormhole)的运行时间重配置技术,该技术适合分布式计算。计算单元是一组数据流,当它经过可重配置的硬件时产生定制的逻辑。

同样位于伯克利的加利福尼亚大学的John Wawraynek和他的同事们也正在开发几种将微处理器与FPGA组合起来的系统,专门的编译软件会处理普通程序代码并为最快的整体性能自动生成机器指令和FPGA配置的组合。这种方法乘机利用时机把处理器和FPGA集成到单块芯片上。

为最快的整体性能自动生成机器指令和FPGA配置的组合。这种方法乘机利用时机把处理器和FPGA集成到单块芯片上。

FPGA决不会取代通用任务的微处理器,但是,可配置计算的原理大概会在高性能计算系统的开发方面扮演越来越重要的角色。对于涉及需要快速适应输入的算法的应用程序来说,FPGA所提供的计算能力使它们成为首选的部件。

此外,可编程处理器与FPGA之间的界线将会变得不明显,未来的FPGA将包含诸如增大的(局部)存储和专用乘法器等功能,这些都是今天微处理器的标准部件;而正在开发的下一代微处理器,其硬件也将支持像FPGA那样的有限数量的重配置。的确,正如与Internet联网的计算机现在能够自动地从网上下载专用软件来执行特定的任务一样,将来的机器可在它们需要时下载新的硬件配置。从现在起的10年内计算装置将包贪软件可编程的硬件与硬件可配置逻辑的高度组合。

决不会取代通用任务的微处理器,但是,可配置计算的原理大概会在高性能计算系统的开发方面扮演越来越重要的角色。对于涉及需要快速适应输入的算法的应用程序来说,FPGA所提供的计算能力使它们成为首选的部件。

此外,可编程处理器与FPGA之间的界线将会变得不明显,未来的FPGA将包含诸如增大的(局部)存储和专用乘法器等功能,这些都是今天微处理器的标准部件;而正在开发的下一代微处理器,其硬件也将支持像FPGA那样的有限数量的重配置。的确,正如与Internet联网的计算机现在能够自动地从网上下载专用软件来执行特定的任务一样,将来的机器可在它们需要时下载新的硬件配置。从现在起的10年内计算装置将包含软件可编程的硬件与硬件可配置逻辑的高度组合。

(张家睿 译 巨浪 校)

请 登录 发表评论