旧金山市的面积有116平方公里,相当于纽约市曼哈顿岛的两倍之多。但是曼哈顿岛的经济产值却令旧金山市自愧不如。造成这一差距的主要原因在于加利福尼亚州是一个地震多发区,因此各单位的人员和设备一般分散在较低的建筑物中,而纽约市的企业却是一个叠一个地聚集在高耸入云的摩天大楼内,其密度要高得多。这种向上扩展而不是向外扩展的开发方式不仅大大提高了房地产的价值,而且也提高了整座城市的产能。

把这样一条思路应用到计算机芯片的微观世界中,可能有助于为半导体工业注入新的活力,是这个最近开始显示出衰老迹象的行业重振雄风。英特尔公司的创始人之一Gorden E. Moore估计,全世界至今为止制造出的晶体管已超过10亿只,而出人意料是的,这些晶体管几乎全都是“贴地”制造的,也就是直接做在硅晶体的表面上。工程师们仅仅通过扩大每块芯片的面积并缩小每个晶体管的尺寸,就取得了使每块微芯片晶体管密度定期翻一倍这一令人难以置信的成就(我们称其为半导体行业的摩尔定律)。不过这样的做法无异于一味建造购物商场而不建造摩天大楼。

现在这种高速发展的情况即将有所改变。原因之一是,据物理学家预测,当控制芯片内信息流动的门电路缩小到相当于电子波长的尺寸后(在硅中电子波长约为10纳米这一量级),摩尔定律将寿终正寝,因为此时晶体管将不再产生晶体管效应。此外,在从当前的技术水平到这一最终极限的发展过程中,一连串令人望而生畏的技术难题已经开始挡道,使工程技术人员头疼不已。进展的步伐已经开始放慢。

值得庆幸的是,我和其他一些工程技术人员最近找到一条途径来克服这些障碍,从而使摩尔定律得以重获新生,甚至还有可能使进展的步伐超过摩尔定律的预测,以更低的成本打造出更强的计算能力。我们已经证明,借助于制造传统半导体芯片所用的那些半导体设备和标准原料以及类似的制造技术,做出由垂直微电路构成的芯片是完全可行的。

Matrix半导体公司是本文作者与半导体科学家P.Michael Farmwald及芯片设计专家Mark C.Johnson1998年在加利福尼亚州圣克拉拉创办的一家企业。目前该公司正在加紧进行把这种“三维芯片”的研究成果转化为商业产品的工作,将在2002年上半年将3维存储电路推向市场。这些电路只是新一代高密度低成本芯片的先锋,它们可望大大降低数字记录载体的成本并使其更加方便,从而取代现有的照相底片和录音磁带。在斯坦福大学和Matrix公司的实验室里,我们还造出了含有垂直逻辑电路的原型装置。有充分的理由相信,即使对于微处理器,垂直电路芯片的应用潜力也是无可限量的。

突破平面的限制

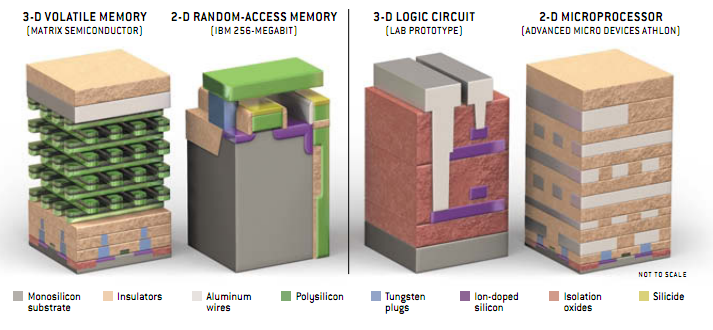

现今最先进的微电路也不完全是2维的。例如英特尔的奔腾4处理器便有7层之多的布线,嵌在绝缘材料组成的电路图案内。然而,有源的半导体区域则只分布在最低层的纯净硅中。

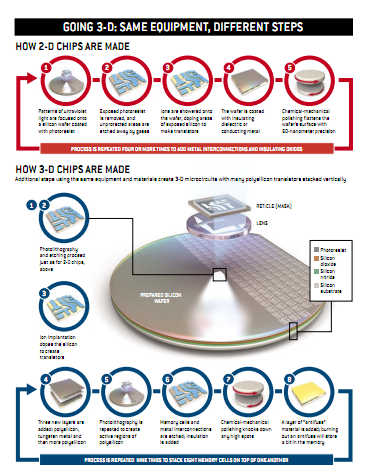

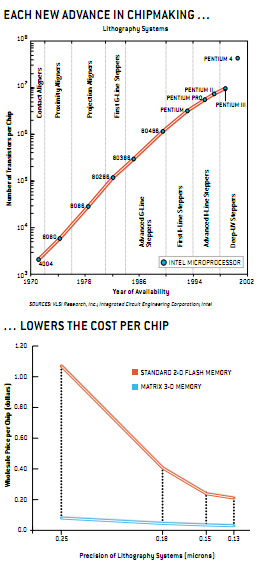

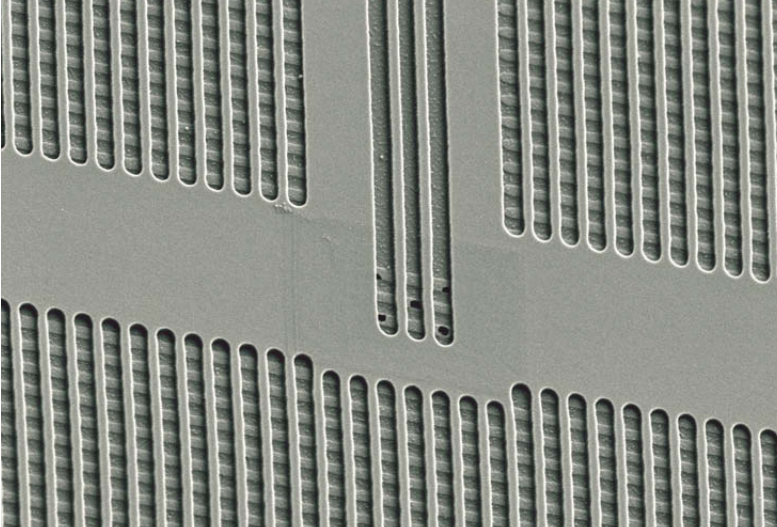

半导体行业的发展之所以至今能一直维持摩尔定律所预测的高速度,其主要法宝在于工程技术人员千方百计地不断改进对硅晶片的利用。材料科学家发明的新方法可以生长出直径达30厘米的巨大硅晶体,而其杂质含量低于10亿分之一。洁净室的机器人把精确计量的掺杂离子注入到从这些晶体切下的硅片中,然后,一项名为光刻法的公益通过光的图案和酸的腐蚀在芯片上划出离子活化区,从而做成晶体管(见下页图)。在一块芯片上做出的晶体管越厚,光的波长就必须越短。传统的水银蒸汽灯已经被深紫外准分子激光器所取代,这种激光器可在芯片上刻出线宽为l30纳米的图像,使一块芯片上做出的晶体管多达10亿只。进一步的改良可使线宽缩小到65纳米,而晶体管可能增加到160亿只。然而,越过这一点之后前面的道路可能就会变得崎岖难行了。最新的极端紫外辐射光刻系统一一它使用波长更短的紫外光——现在才刚刚开始在实验室工作。这类系统仍然存在不少棘手的问题。如果历史能给被们点什么启示的话,那就是工程师多半将会扫除这些障碍。克服这些技术问题将带来巨大的经济利益;利之所在,不愁无人攻关。但是随着障碍的与日俱增,进展的步伐可能会显著放慢。美国半导体行业协会公布了一份正式的“路线图”,预测芯片的面积每年将增长4%到5%,而历史上面积的增长度一直维持在每年l5%左右。芯片的线宽以前是每隔两年减小30%,但现在可能要每隔3年才减小30%了。即使按这一较低的进展速度来预测,摩尔法则也极有可能在2010年到2020年之间的某个时候撞在那道不可逾越的最终界线上,无计可施了。

但是一项重要的因素始终没有出现多大的变化,这就是,半导体不动产的成本一直维持在每加工1英亩的硅l0亿美元左右。既然如此,硅芯片开发商们为何不使出向高处发展这样一着看来再明显不过的招数呢?最简单的原因是,从单晶硅上切割下来的芯片其原子是完全排列整齐的,而只有用这样的原子制出的晶体管才是速度最快、工作最可靠的。

一旦我们在半导体硅片上覆着一层绝缘氧化物或金属导线,我们就没有什么现成的办法来重现下面的结晶模式了——这就好比是用地毯盖住了镶木地板之后,又想再跟镶木地板的图案对齐是难上加难一样。沉积在非结晶表面上的硅通常将是完全无序的无定形硅。通过适当的热处理我们可以设法促使硅形成一些微小的单晶岛(“晶粒”),但是在各晶粒之间的边界上,一行行井然有序的原子突然以不规则的角度挤在一起。杂质碰到这些障碍后可能堆积起来,使得被夹在其中的晶体管或存储单元短路。多年来,这类无定形硅与多晶硅器件的性能始终不见起色,因此,除了太阳能电池这类最简单的产品外,对于要求较高的场合,没有人会认真考虑采用上述产品。

不过,上世纪80年代初期曾有一些科学家杞人忧天,担心摩尔定律即将失效,这例恐慌情绪刺激人们掀起了一股制作3维微电路的热潮。在这类电路中晶体管跨越的是垂直的硅塔而非水平的硅桥。斯坦福大学的James F.Gibbons及其他一些研究人员使用了激光束来改进沉积在非硅基底上的硅薄膜的质量。还有一些研究人员则尝试把传统的2维芯片一块接一块地叠起来。遗憾的是,前一种方法的速度太慢,而后一种方法则成本过高,缺乏经济上的竞争力。这样传统的芯片制造法有惊无险,依然坚守自己的阵地,而工程师们则对垂直电路之类的东西不再抱什么奢望了。

旧瓶装新酒

1997年我和Farmwald再次开始探索3维芯片。这一回我们意识到两项为其他用途而开发出来的关键的起动技术,无意中却为3维芯片的发展铺平了道路,使得它第一次成为真正切实可行的技术。这两项技术中第一项是一种淀积多晶硅的方法,它使每个单晶岛都大得足以包容许多存储单元或晶体管。第二项则是一种把每层新覆盖的材料弄平坦的方法,这样芯片就不会参差不齐地突起,宛如喝醉了酒的砌砖师傅砌起的塔楼。

第一项突破应该归功于平板显示器行业。该行业的工程师发现了如何用覆盖在一大块无定形基底(他们用的基底是玻璃,而我们的基底则是其他材料)上的薄膜制造出数百万个晶体管。现在几乎每一台便携式电脑的显示屏上都是薄膜晶体管在唱主角。这项技术的奥秘之一就是在400℃左右的温度下把硅淀积成一层极平整光滑的无定形薄膜,然后在高于500℃的温度下把整块硅片均匀地烘烤几分钟。这样一种处理就把薄膜转变成了多晶硅,其内分布着直径为一微米或更大的规则的结晶区域。液晶显示屏只需要一层晶体管,但制造这些显示屏的机器同样可以制造多层器件。

第二项关键的启动技术称为化学机械抛光法(CMP chemical-mechanical polishing),它是IBM公司研究实验室上世纪80年代后期开发出来的成果。当时芯片设计师们认为在硅片上面覆盖两到三层金属是相当冒险的做法,因为新加上的每一层都会有凹凸不平之处,而这些凹凸不平将会使光刻图案难于聚焦。

为了消除每一层中的鼓胀,工艺专家们借用了透镜制造商用来磨光镜面的一项秘诀。这一基本方法用在了所有的因特尔486系列处理器上。每覆盖一层硅、金属或绝缘氧化物之后,就把硅片面朝下放置于一块垫上。两根轴分别带动垫与硅片沿相反方向转动,同时一种含有研磨材料及活性碱性药物的浆液被注入二者之间。只需经过几分钟的抛光,硅片的不平整度就降低到不超过50纳米,完全适合于进行下一步加工。随着CMP设备的不断改进,眼下在微芯片设计中采用7层到8层金属已经是家常便饭;制造层数更多的芯片也是易如反掌的事情,唯一的要求是要有耐心。

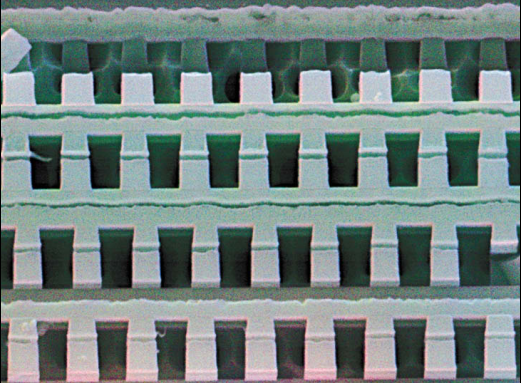

我们直接利用这些2维技术来制作3维电路,其方法是把许多层多晶硅(以及绝缘层和金属层)一层接一层地覆盖在标准的硅片上,每覆盖一层后就将其表面抛光。虽然电子在多晶硅中的运动不及单晶硅中那么快捷,但我们的研究已经开发出了比较满意的3维晶体管,其电子迁移率达到了同型2维晶体管的90%至95%。

把晶体管沿垂直方向堆起来为我们提供了一种解决某些老大难问题的办法,这些问题已经使摩尔定律处于岌岌可危的境地。例如,随着购物商场式的芯片不断向外扩展,光刻图案的边缘越来越难以保持准确的聚焦了。而连接传统芯片中相距较远的区域的导线也越变越长.由此产生的延迟导致芯片性能的下降,并使其设计变得更加复杂。

不断缩小的电路也带来其他一些问题。控制电极下方薄薄的一层绝缘物对于晶体管的正常运行至关重要。在最先进的2维晶体管中,这一层氧化硅绝缘物的厚度只有3纳米,相当于二十几个原子。各晶体管之间这一厚度的差异不能超过一到两个原子。半导体行业通常都能达到这一要求,因为生产出超薄薄膜要比蚀刻出超细沟道容易得多。但是可能不存在什么实用的办法来使这些绝缘层的厚度大大变薄,因为量子隧道效应所形成的电针使这些绝缘层的绝缘性能越来越差。或许我们很快就必须用某种其他材料来取代二氧化硅,不过眼下厂商们尚未就应该用何种材料取得共识。

为了解决这些问题,研究人员已经提出了多种新颖的芯片设计方案。大多数方案都彻底抛弃了硅,而代之以各种新奇的材料,如有机聚合物、碳富勒烯、铜化合物、铁电体或磁合金等等。但如果半导体行业与硅一刀两断,那就意味着50余年间打造起来的一座价值连城的知识宝库将失去用武之地,而上千亿美元的投资也将付之东流。

反观3维电子设计方法则具有种种优势,例如不需要引入新的材料,可以充分利用半导体行业对薄膜设备和CMP设备的巨额投资,等等。由于生产并加工超纯硅锭的费用极其昂贵,因此硅的成本在很大程度上是与所占用的面积(而非体积)成比例。这样,与传统芯片相比,采用垂直电路的芯片可以使制造费用降低百分之九十以上。而且,随着芯片层数的递增,3维器件的电路密度的增长速率至少将可以保持摩尔定律所预测的速度。

数字薄膜及其他

传统上半导体厂家部是先通过生产存储器件来找到并排除新的制造工艺所存在的问题,然后再开始大批生产更复杂的芯片(如逻辑电路)。存储芯片是数量庞大的存储单元所构成的阵列,这些单元的构造非常简单,因此对技能的要求比较低,需要解决的问题也比较少。

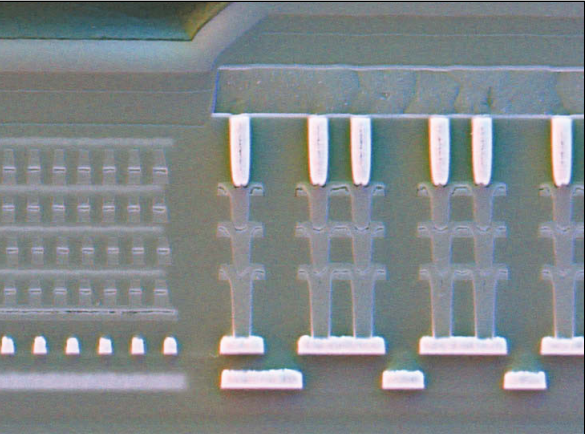

这正是今年晚些时候我们Matrix公司将推出一种由8层存储单元构成的3维存储芯片时(见下图)所要遵循的方针。与微机中使用的内存条(RAM)不同,这些芯片采用极其简单的存储元,使得它们与薄膜颇为相似,一旦写上后就擦不掉了。此类芯片用作数字摄影及音响品中的低成本记录载体。作为垂直微芯片的开山鼻祖,这种存储器件有5.12亿个存储单元,其容量之大可以存储1个小时的高品质音乐节目(通过数据压缩)及几百幅照片(每幅均有100万个象素)。这种芯片的存储能力还将进一步增加,而其单位成本则相应下降。我们已经证明由12层存储单元构成的器件是可行的,而16层高的芯片看来也指日可待。

我们还在实验室里验证了复杂得多的3维微电路,包括静态随机存取存储器(RAM)、逻辑门乃至可擦可编程序只读存储器(EPROM)等。这些3维电路目前仍在最初步的开发阶段上,但它们是最基本的结构单元,只要有了它们,把任何一种平面电路——如动态随机存取存储器、非易失性存储器,无线电收发装置以及微处理器等——改造成3维形式的问题也就迎刃而解了。这些电路中的晶体管是立式的,可以做得非常微小,因为它们的内道是用极薄的薄膜制成的,这些薄膜的精度比紫外光刻出的沟道高10倍。

工程技术方面的所有进展肯定都存在局限性,而且是有得必有失,这种新的制造方法自然也例外,在垂直微电路中,一部分存储单元或晶体管将正好跨越多晶硅晶粒之间的边界,因此我们必须使用错误检测与校正例行程序(例如用于音乐光盘的这类例行程序),同时找到适当的方法来使信号绕过出错的路径发送。容错计算的原理虽然已是众所周知,但微芯片本身并没有装入这类系统。大多数平面微电路没有必要使用它们,而且这类系统过于繁锁,不适合用于平面电路中。3维微电路则必须使用纠错技术,但凑巧的是3维处理大大节约了成本,因此3维微电路使用纠错技术从成本效益的角度来看仍是可行的。

3维微电路必须作出的另一项牺牲是速度。现代薄膜品体管的运行速度通常为单晶硅晶体的一半左右。不过,如果比较整个电路的性能,那么二者的差距就没有那样大了,因为布置在3维空间中的元件其导线要短得多。现在许多研究人员正在探索各种方法以进一步缩小两者间的差距。

3维芯片除了这些特有的问题之外,还面临着一些基本上与传统平面电路如出一辙的挑战——某些问题只是因为发展速度比摩尔定律预测的更快而暴露得更早。高密度的3维器件因为其表面积减小,因此如何散热可能成了最棘手的问题。现代微处理器的功率密度已经超过了一般炉灶上的燃烧器的功率密度。现有的一些散热方法——例如降低电压或者有选择地启动一部分电路等——难以有效地排除所有这些热量,因此散热问题可能成为进一步改善高密度3维电路性能的拦路虎,除非采用更先进的冷却技术。幸运的是,最新式的微型制冷器现在可以耗散每平方毫米200瓦的热量,而其消耗的功率只有l瓦左右。因此,热极限现在还不是根本的障碍。

散热肯定还大有潜力可挖。靠流体冷却的人脑的尺寸大大超过了目前构想的任何一种3维电路的大小,但它只消耗区区25瓦的功率。反观微电路的情况则是只有2.2平方厘米大的奔4处理器却要消耗80瓦之多的功率。如果我们无法解决散热问题,则我们就不能排除这个问题在将来可能最终严重限制3维电路性能的提高。不过,历史经验告诉我们,车到山前必有路,在经济利益强有力的驱动下,富有创造性的解决方法的出台只是迟早的事情。

设法使摩尔定律的有效期哪怕只延长几年,也会产生意义深远的影响。30年来,芯片制造商一直不遗余力地设法在一个平面内打造出尺寸越来越小的结构。而将来微电路的发展似乎不可避免地要采取两路出击的策略,一方面继续在平面内开拓,另一方面则要向空间挺进。构筑3维芯片的技术不但可行,而且实用,它的效益之大令人垂涎三尺,想不动心都不可能了。

概述:3维微电路

l 摩尔定律——该定律支出作为信息产业支柱的硅基微芯片的复杂程度以一定规律稳步增长——正在接近物理学法则所决定的最终极限。用新型半导体材料来代替硅其费用将是极其昂贵的。

l 工程技术人员不久前找到一种办法来延长摩尔定律的有效期,甚至还可能使微电路性能的增长速率大大超过摩尔定律的预测。工程师们已经设计出并开始批量生产多层芯片,这些芯片中的半导体电路元件不再仅仅是布置于平面上,而是同时也向空中扩展。

l 装有这类3维微芯片的首批产品——存储片——定于2002年晚些时候问世,其价格非常便宜,可用作数字胶片及录音载体。

【刘山岷/译 曾少立/校】

请 登录 发表评论